Rambus推出最新CXL 2.0控制器,内置业界领先零延迟IDE安全模块

|

新闻摘要:

- 通过集成的IDE模块实现超高速数据传输中的安全性,帮助数据中心基础设施实现无与伦比的性能

- 为CXL.mem和CXL.cache协议提供零延迟数据加密功能

- 与Rambus CXL 2.0 PHY集成,构建完整的CXL互连子系统

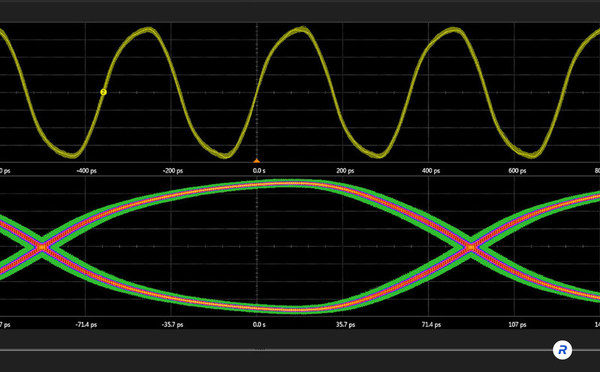

北京2021年10月26日 /美通社/ -- 作为业界领先的芯片和IP核供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布推出内置完整性和数据加密(IDE)模块的Compute Express Link™(CXL)2.0和PCI Express®(PCIe)5.0控制器在CXL协议上实现超高速数据传输中的安全性,对于解决数据中心基础设施中的带宽瓶颈至关重要IDE模块可监控并防止对CXL和PCIe链路的物理攻击CXL需要极低的延迟,才能为目标用例实现load-store内存架构和缓存一致性链路这款突破性的控制器由Rambus最近收购的PLDA工程团队研发,凭借内置的零延迟IDE模块,可支持在32 GT/s的最高速率下实现最先进的安全性和性能。

内置IDE安全模块的Rambus CXL 2.0控制器

Rambus首席运营官范贤志(Sean Fan)表示:“要在数据密集型应用中成功启用CXL使用模式,例如在处理器和附加的AI加速器之间共享内存,需要在超低延迟的前提下实现数据传输的安全性此次零延迟安全控制器的推出,证明我们在最近收购PLDA之后,具备了加速开发CXL解决方案的能力,同时彰显了我们在提供集成式接口和安全IP解决方案方面独一无二的优势地位”

此次发布的Rambus CXL 2.0和PCIe 5.0控制器均内置IDE模块,采用256位AES-GCM(高级加密标准,伽罗瓦/计数器模式)对称密钥分组密码算法,可确保通过CXL和PCIe链路传输的数据流的机密性、完整性和重放攻击保护,并简化芯片设计人员和安全架构师的工作此类安全功能对于各种数据中心计算应用尤为必要,如AI/ML和高性能计算(HPC)等等。

主要功能包括:

- 通过零延迟IDE模块确保CXL.mem和CXL.cache的安全性

- 有效防护物理安全攻击,将安全漏洞所引发的安全、财务和品牌声誉风险降至最低

- Rambus CXL 2.0和PCIe 5.0控制器预集成的IDE模块,可提升产品成功率并缩短产品上市时间

- 控制器可与Rambus CXL 2.0PHY以及PCIe 5.0 PHY配合使用,以构建完整的CXL 2.0和PCIe 5.0互连子系统

更多信息:

关于内置IDE模块的Rambus CXL 2.0控制器和PCIe 5.0控制器,如需了解更多信息,请访问我们的网站:

CXL 2.0子系统:

- 内置IDE模块的CXL 2.0控制器

- CXL 2.0 PHY

PCIe 5.0子系统:

- 内置IDE模块的PCIe 5.0控制器

- PCIe 5.0 PHY